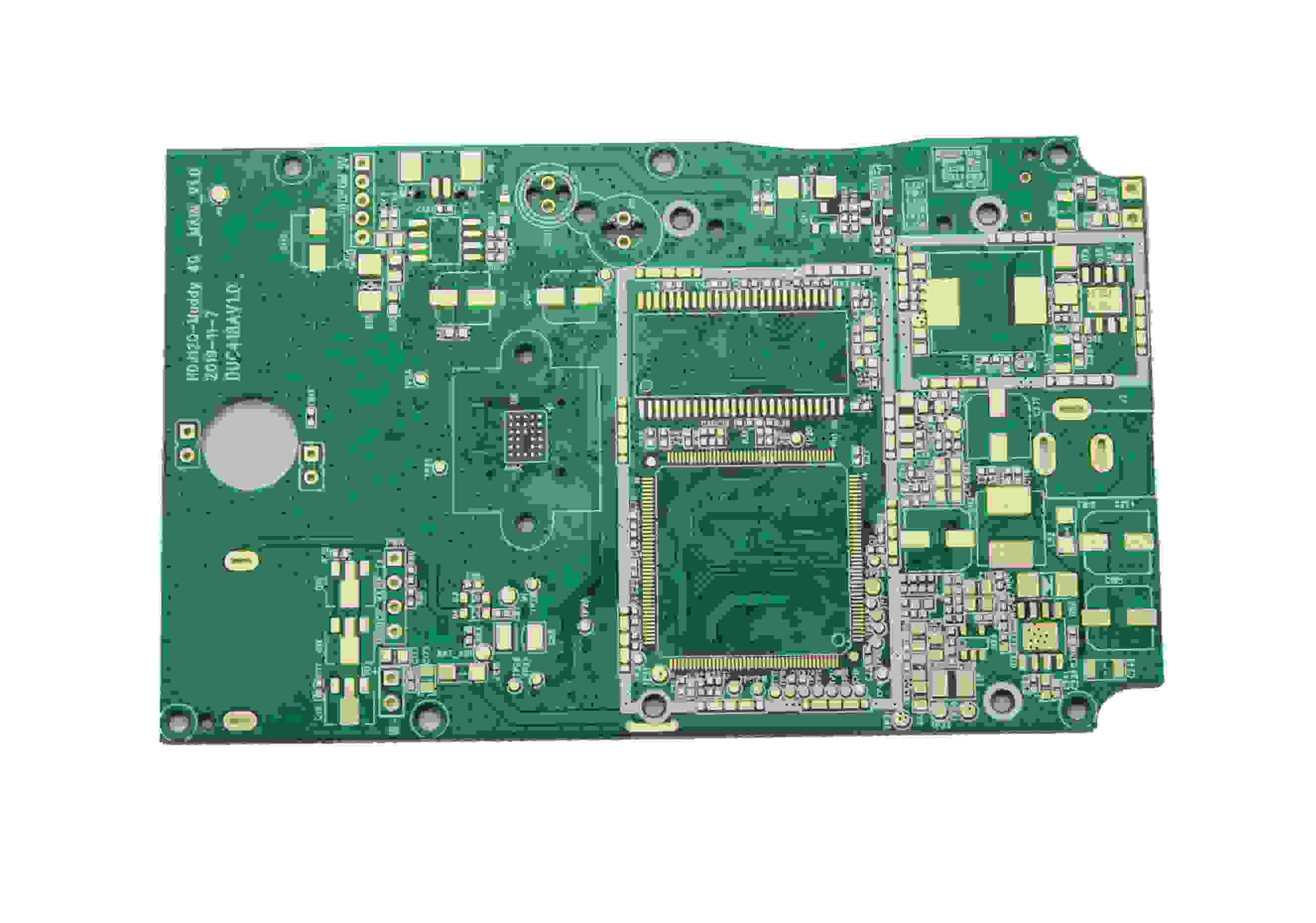

PCB廠:基于Cadence的高速PCB設(shè)計(jì)分享

1 簡(jiǎn)介

隨著人們對(duì)通信需求的不斷提高,要求信號(hào)傳輸和處理的速度越來(lái)越快。 相應(yīng)的高速PCB也應(yīng)用得越來(lái)越廣泛,設(shè)計(jì)也越來(lái)越復(fù)雜。高速電路有兩層含義:一是高頻化。 一般認(rèn)為,數(shù)字電路的頻率達(dá)到或超過(guò)45MHz至50MHz,工作于該頻率的電路已占整個(gè)系統(tǒng)的三分之一,稱為高速電路。 信號(hào),當(dāng)信號(hào)的上升時(shí)間小于信號(hào)傳輸延遲的6倍時(shí),該信號(hào)被認(rèn)為是高速信號(hào),并且該考慮與信號(hào)的具體頻率無(wú)關(guān)

2 高速PCB設(shè)計(jì)的基本內(nèi)容

高速電路設(shè)計(jì)在現(xiàn)代電路設(shè)計(jì)中所占的比重越來(lái)越大,設(shè)計(jì)難度也越來(lái)越高。 其解決方案不僅需要高速器件,更需要設(shè)計(jì)者的智慧和精心勞動(dòng)。 解決現(xiàn)有高速電路問(wèn)題必須針對(duì)具體情況認(rèn)真研究分析一般來(lái)說(shuō)主要包括三個(gè)方面:信號(hào)完整性設(shè)計(jì)、電磁兼容設(shè)計(jì)和電源完整性設(shè)計(jì)

2.1 信號(hào)完整性設(shè)計(jì)

信號(hào)完整性是指信號(hào)線上信號(hào)的質(zhì)量,信號(hào)完整性好的信號(hào)是指在需要的時(shí)候具有所需要的電壓電平值,信號(hào)完整性差不是單一因素造成的,而是板級(jí)設(shè)計(jì)中多種因素造成的,特別是 在高速電路中,所用芯片的開(kāi)關(guān)速度太快,終端元件布局不合理,電路互連不合理,都會(huì)造成信號(hào)完整性問(wèn)題。 具體包括串?dāng)_、反射、過(guò)沖和下沖、振蕩、信號(hào)延遲等

2.1.1 串?dāng)_

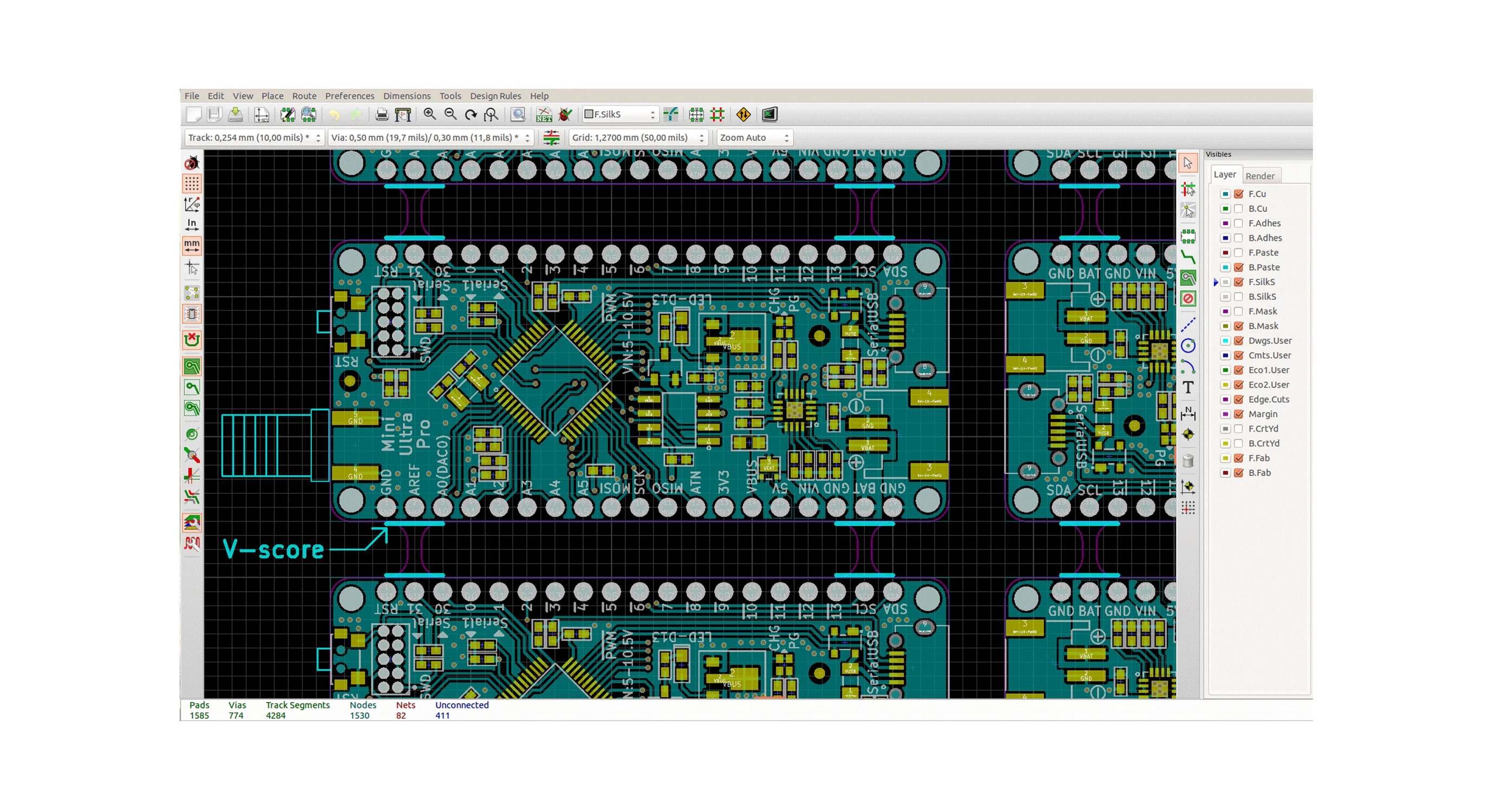

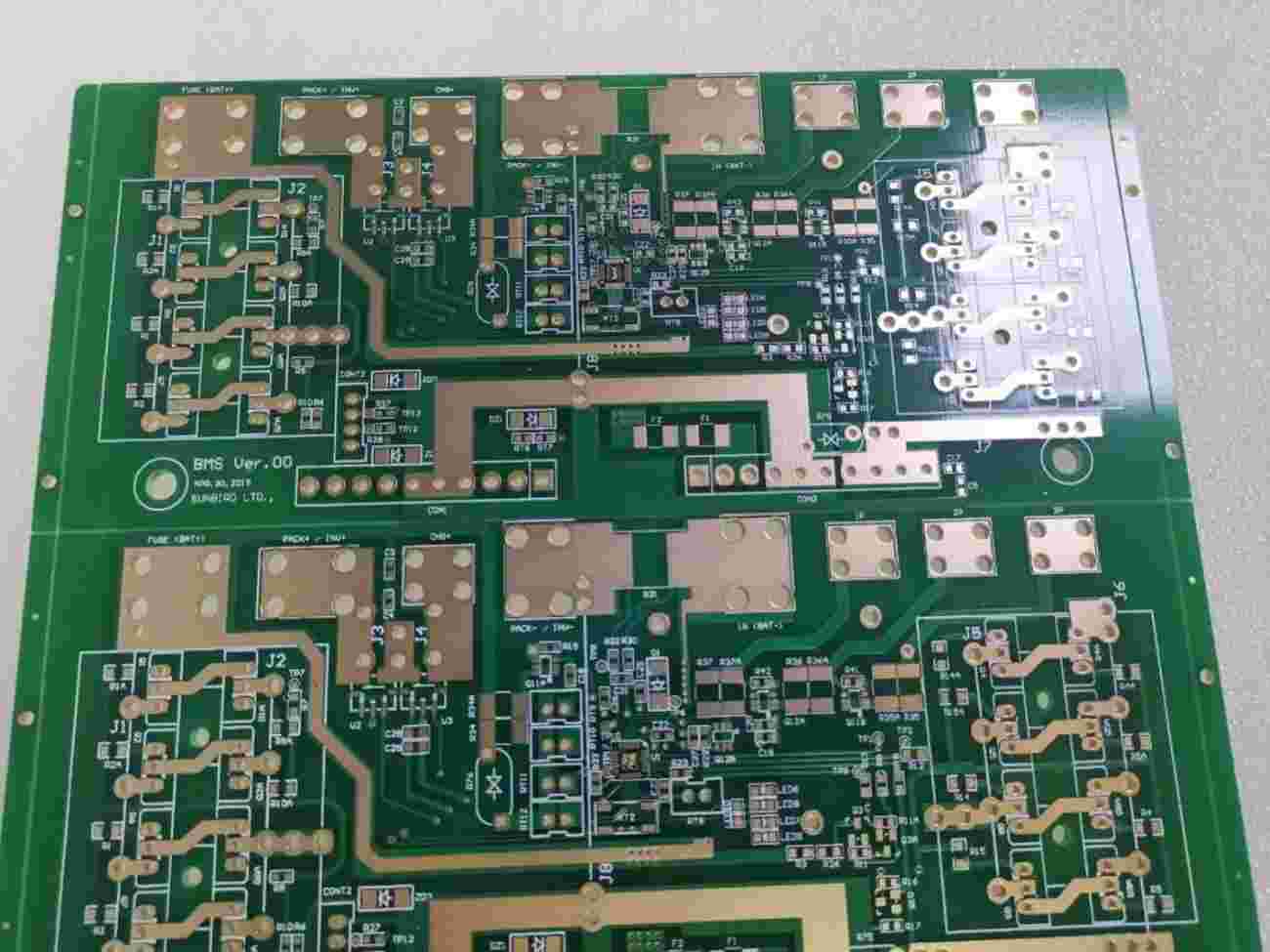

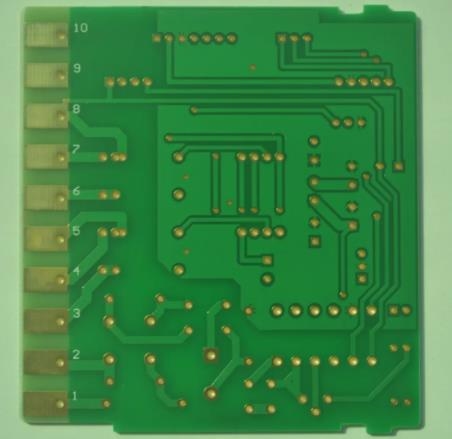

串?dāng)_是兩條相鄰信號(hào)線之間不必要的耦合。 信號(hào)線之間的互感和互電容會(huì)導(dǎo)致線路上出現(xiàn)噪聲。 因此也分為感性串?dāng)_和容性串?dāng)_,分別引起耦合電流和耦合電壓。 當(dāng)信號(hào)的邊沿速率小于1ns時(shí),應(yīng)考慮串?dāng)_如果有交變信號(hào)電流通過(guò)信號(hào)線,就會(huì)產(chǎn)生交變磁場(chǎng),相鄰信號(hào)線會(huì)感應(yīng)出信號(hào)電壓。 一般情況下,PCB層數(shù)參數(shù)、信號(hào)線間距、驅(qū)動(dòng)器和接收器電氣特性、信號(hào)線端接方式等對(duì)串?dāng)_都有一定的影響。在CADence的信號(hào)仿真工具中,可以將6條耦合信號(hào)線 同時(shí)模擬串?dāng)_后。 可以設(shè)置的掃描參數(shù)包括:PCB的介電常數(shù)、介質(zhì)的厚度、銅沉積的厚度、信號(hào)線的長(zhǎng)度和寬度、信號(hào)線的間距。在仿真過(guò)程中,還必須指定受傷的信號(hào)線,即: 排查其他信號(hào)線對(duì)該線路的干擾。 將激勵(lì)設(shè)置為恒高或恒低,這樣就可以測(cè)量出該信號(hào)線上其他信號(hào)線的感應(yīng)電壓之和,從而得到滿足要求的最小間距和最大平行長(zhǎng)度

2.1.2 反思

反射就像我們知道光通過(guò)不連續(xù)介質(zhì)時(shí),會(huì)反射一些能量回來(lái),即信號(hào)在傳輸線上的回聲。 此時(shí)信號(hào)功率還沒(méi)有完全傳輸?shù)截?fù)載,還有一部分被反射回來(lái)。在高速PCB中,導(dǎo)線必須相當(dāng)于傳輸線。 根據(jù)傳輸線理論,如果源端和負(fù)載端具有相同的阻抗,則不會(huì)發(fā)生反射。 兩者之間的阻抗不匹配會(huì)引起反射,負(fù)載會(huì)將部分電壓反射回源端。 根據(jù)負(fù)載阻抗和源阻抗之間的關(guān)系,反射電壓可能為正或?yàn)樨?fù)。如果反射信號(hào)非常強(qiáng)并疊加在原始信號(hào)上,則很可能會(huì)改變邏輯狀態(tài)并導(dǎo)致接收數(shù)據(jù)出現(xiàn)錯(cuò)誤 。 如果時(shí)鐘信號(hào)不是單調(diào)的,則可能會(huì)導(dǎo)致誤觸發(fā)。一般布線幾何形狀、不正確的電線端接、通過(guò)連接器的傳輸以及電源層的不連續(xù)性都會(huì)導(dǎo)致此類反射。此外,通常有一個(gè)輸出和多個(gè)接收器。 這時(shí),不同的布線策略產(chǎn)生的反射對(duì)每個(gè)接收器的影響是不同的。 因此,布線策略也是不可忽視的因素。 PCB加工及PCBA加工廠商將講解基于Cadence的高速PCB設(shè)計(jì)分享。

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱