工程師對高速PCB設(shè)計有何解釋?

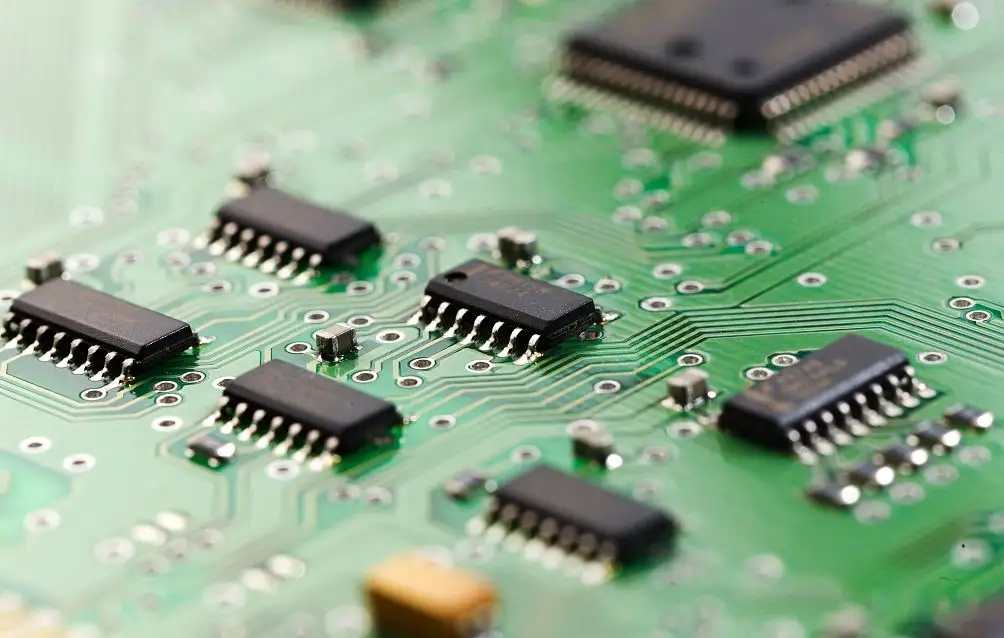

大多數(shù) PCB 都被認為存在某種類型的信號完整性問題的風(fēng)險,這些問題通常與高速數(shù)字設(shè)計相關(guān)。 高速 PCB 設(shè)計和布局側(cè)重于創(chuàng)建不易受到信號完整性、電源完整性和 EMI/EMC 問題影響的電路板設(shè)計。 盡管沒有任何設(shè)計能夠完全避免這些問題,但這些問題可以減少到微不足道的程度,并且不會在最終產(chǎn)品中造成性能問題。

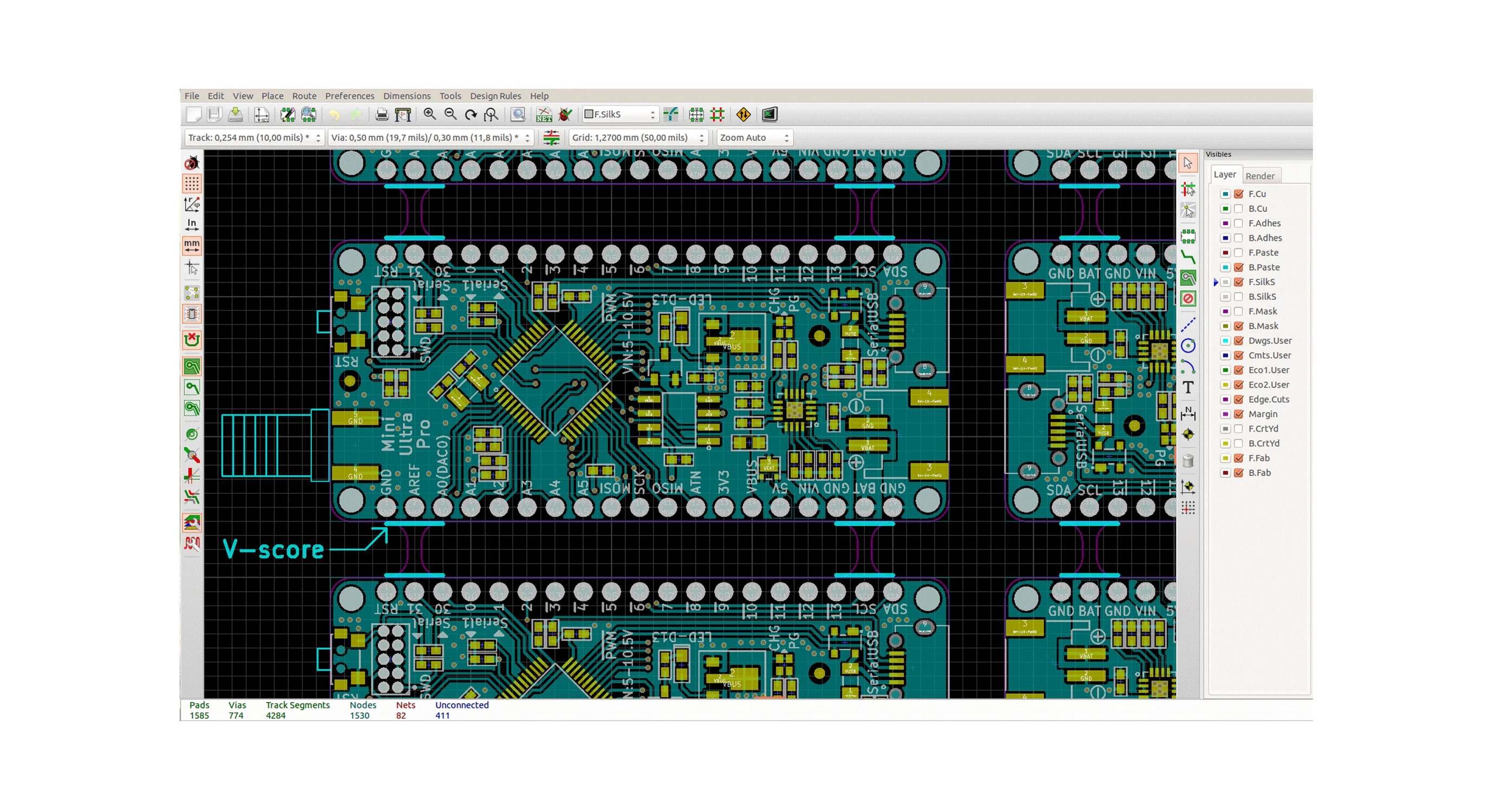

創(chuàng)建原理圖并準(zhǔn)備過渡到電路板布局后,您需要使用 PCB 設(shè)計工具中的特定功能來進行正確的布局和布線。 在 PCB 設(shè)計軟件中,您將有機會在層堆疊中準(zhǔn)備電源和接地平面布局、計算布線的阻抗分布以及查看堆疊 PCB 材料選項。 高速設(shè)計的大多數(shù)方面都圍繞 PCB 堆棧設(shè)計和布線,以確保信號和電源完整性,而正確的 ECAD 軟件可以幫助確保在這些領(lǐng)域取得成功。

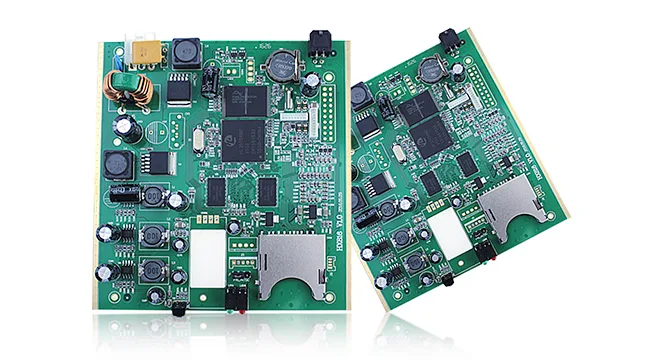

高速設(shè)計是指使用高速數(shù)字信號在組件之間傳輸數(shù)據(jù)的系統(tǒng)。 高速數(shù)字設(shè)計和具有較慢數(shù)字協(xié)議的簡單電路板之間的分界線并不明確。 將特定系統(tǒng)表示為“高速”的一般指標(biāo)是系統(tǒng)中使用的數(shù)字信號的邊沿速率(或上升時間)。 大多數(shù)數(shù)字設(shè)計同時使用高速(快邊沿速率)和低速(慢邊沿速率)數(shù)字協(xié)議。 在當(dāng)今嵌入式計算和物聯(lián)網(wǎng)時代,大多數(shù)高速 PCB 都具有用于無線通信和網(wǎng)絡(luò)的 RF 前端。

雖然所有設(shè)計都是從原理圖開始,但高速PCB設(shè)計的主要部分集中在互連設(shè)計、PCB堆疊設(shè)計和布線上。 如果您在前兩個領(lǐng)域取得成功,那么您很可能在第三個領(lǐng)域取得成功。 閱讀以下部分,了解如何開始高速設(shè)計以及 PCB 設(shè)計軟件的重要作用。

規(guī)劃 PCB 堆疊和阻抗

您為高速電路板創(chuàng)建的 PCB 堆棧將決定阻抗和接線的難易程度。 所有 PCB 層均包含一組專用于高速信號、電源和接地層的層。 在層內(nèi)分配層時需要考慮以下幾點:

電路板尺寸和網(wǎng)絡(luò)數(shù)量:電路板有多大以及在PCB布局中需要布線多少個網(wǎng)絡(luò)。 物理尺寸較大的電路板可能有足夠的空間讓您在整個 PCB 布局中進行布線,而無需使用多個信號層。

布線密度:當(dāng)網(wǎng)絡(luò)較多且電路板尺寸僅限于較小區(qū)域時,您可能沒有足夠的空間在表層周圍布線。 因此,當(dāng)布線更近時,您將需要更多的內(nèi)部信號層。 轉(zhuǎn)到較小的一個

接口數(shù)量:有時,根據(jù)總線的寬度(串行和并行)和電路板的尺寸,每層上僅布線一個或兩個接口是一個很好的策略。 將高速數(shù)字接口中的所有信號保持在同一層,以確保所有信號都能看到一致的阻抗和偏轉(zhuǎn)。

低速和射頻信號:您的數(shù)字設(shè)計中是否有低速數(shù)字或射頻信號? 如果是這樣,它們可能會占用可用于高速總線或組件的表面空間,并且可能需要額外的內(nèi)層。

電源完整性:電源完整性的基石之一是針對大型 IC 所需的每個電壓級別使用大型電源層和接地層。 它們應(yīng)放置在相鄰層上,以幫助確保高平面電容,以通過去耦電容器支持穩(wěn)定的電源。

PCB 材料選擇、層數(shù)和厚度

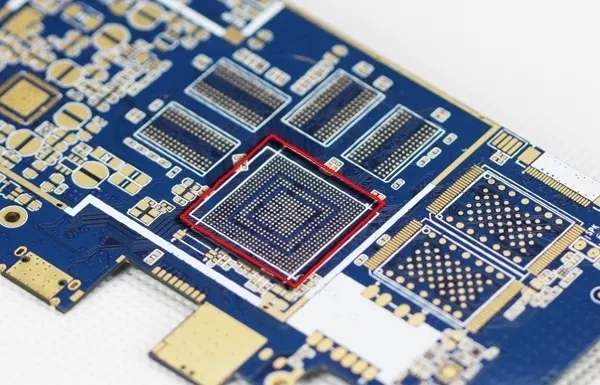

在設(shè)計 PCB 堆棧之前,請考慮容納設(shè)計中所有數(shù)字信號所需的層數(shù)。 有很多方法可以確定這一點,但這些方法取決于一些數(shù)學(xué)計算和一些過去高速電路板設(shè)計的經(jīng)驗。 除了上面列出的考慮層數(shù)的要點之外,具有 BGA/LGA 封裝的大型高速 IC 還可以確定所需的電路板尺寸。 進行BGA扇出時,每個信號層一般可以放置2根線,并保證在搭建堆疊時將電源層和接地層包含在層數(shù)中。

FPGA 上的 BGA 扇出具有大多邊形,用于高速設(shè)計中的供電。

FR4級材料通常可用于高速數(shù)字設(shè)計,只要元件之間的路線不太長。 如果路由確實變得太長,您的高速通道中將會出現(xiàn)太多損耗,并且通道接收端的組件可能無法恢復(fù)信號。 選擇材料時要考慮的主要材料特性是PCB層壓板的損耗角正切。 通道幾何形狀也將決定損耗,但具有較低損耗角正切的 FR4 層壓板通常是較小電路板的良好起點。

如果您的線路太長,您可能需要更專業(yè)的材料作為高速信號的基材。 基于 PTFE 的層壓板、分散玻璃層壓板或其他特殊材料系統(tǒng)非常適合支持大型高速數(shù)字板,其中布線較長且需要低插入損耗。 用于小型高速 PCB 的入門級高 Tg 層壓材料的良好組合是 370HR。 對于較大的電路板,Megtron 或 Duroid 層壓板是不錯的選擇。 在繼續(xù)之前,請咨詢您的制造商,以確保您選擇的材料和推薦的疊片是可制造的。

阻抗控制

只有在創(chuàng)建推薦的堆棧并與制造商驗證后才能確定阻抗。 制造商可能會建議對 PCB 堆棧進行修改,例如替代 PCB 材料選項或?qū)雍穸取?一旦您獲得了要使用的層的許可并最終確定了層的厚度,您就可以開始計算阻抗值。

阻抗通常使用公式或計算器以及場求解器工具來計算。 設(shè)計中所需的阻抗將決定傳輸線的尺寸以及與附近電源或接地層的距離。 以下工具可用于確定傳輸線寬度:

IPC-2141 和 Waddell 的公式:這些公式提供了阻抗估計的起點,并且它們在較低頻率下產(chǎn)生準(zhǔn)確的結(jié)果。

2D/3D 場求解器實用程序:場求解器用于求解您為高速板定義的傳輸線幾何形狀中的麥克斯韋方程。

將層堆棧管理器與場解算器結(jié)合使用將為您提供最準(zhǔn)確的結(jié)果,同時考慮銅粗糙度、蝕刻、不對稱線對準(zhǔn)和差分對。 計算出線路的阻抗曲線后,需要在布線工具中將其設(shè)置為設(shè)計規(guī)則,以確保線路具有所需的阻抗。

高速板傳輸線設(shè)計的阻抗計算。 Altium designer 中的層堆棧管理器包含一個用于計算銅粗糙度的阻抗計算器。

大多數(shù)高速信號協(xié)議(例如PCIe或以太網(wǎng))都使用差分對布線,因此需要通過計算布線寬度和間距來設(shè)計特定的差分阻抗。 場求解器工具是計算任何幾何形狀(微帶線、帶狀線或共面)的差分阻抗的最佳工具。 場解算器實用程序的另一個重要結(jié)果是傳播延遲,它用于在高速布線期間強制進行長度調(diào)整。

高速PCB布局規(guī)劃

對于高速 PCB 布局中元件的放置位置,沒有具體的規(guī)則或標(biāo)準(zhǔn)。 一般來說,將最大的CPU IC放置在電路板中心附近是一個好主意,因為它通常需要以某種方式連接到電路板上的所有其他組件。 直接連接到中央處理器的較小的 IC 可以放置在中央 IC 周圍,以便組件之間的布線可以保持短而直接。 然后可以將外圍設(shè)備放置在電路板周圍以提供所需的功能。

當(dāng)主控制器IC放置在電路板中心附近,而其他高速外設(shè)放置在其周圍時,高速布局是最佳的。 這也是主板將大型處理器放置在主板中央的原因之一。 Altium Designer 中的 MiniPC 項目將其 PCIe、DDR4、USB 3.0 和以太網(wǎng)外設(shè)放置在中央 FPGA SoC 周圍,因此布線更加容易。

放置元件后,您可以設(shè)置設(shè)計工具來幫助您開始設(shè)計布線。 這是高速電路板設(shè)計的敏感部分,因為不正確的接線會損害信號完整性。 然而,如果前面的步驟正確完成,則更容易實現(xiàn)信號完整性。 您應(yīng)該在 PCB 設(shè)計規(guī)則中設(shè)置阻抗曲線,以便設(shè)計中的任何布線都以正確的寬度、間隙和間距放置,以在布線過程中保持受控的阻抗。

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱